矽光子市場風起雲湧,Marvell在2025/12/2宣布以32.5億美元收購 Celestial AI,並明確把矽光子視為強化資料中心客製晶片互連能力的關鍵,甚至給出光子產品在未來幾年貢獻營收的時間表,反映大廠已用併購加速卡位。同時,產業也開始展示可商品化的光I/O子系統:Alchip與Ayar Labs在TSMC 歐洲OIP 論壇公開基於TSMC COUPE平台的光連結解決方案,將矽光子光引擎與電介面/UCIe 轉換晶粒做成可整合的子系統,凸顯矽光子正沿著 chiplet 與先進封裝生態系加速落地。而從市場研究觀點,Yole也指出矽光子與共同封裝光學(CPO)正成為下一代 AI 驅動資料基礎建設的核心,並預期CPO的大規模部署時間窗落在 2028–2030,意味著短期市場雖然以導入與驗證為主,但中期將進入結構性量能成長。

生成式AI帶來的並不只是演算法革命,更是資料中心基礎架構的全面更新。隨著AI模型參數與訓練資料規模呈指數成長,GPU叢集的功率密度與節點數量急速增加,高速互連逐漸成為整體效能與能耗的瓶頸。現代GPU機櫃往往單機櫃就超過100 kW功率,與過去以CPU為主的傳統伺服器機櫃相比,能源與散熱壓力已是完全不同的量級。

在這樣的背景下,AI基礎建設朝Scale-Up與Scale-Out雙路徑演進:一方面提升單一GPU節點與機櫃的算力密度,另一方面則以更多節點構成更大的叢集。OpenAI與NVIDIA、AMD、Broadcom等在 2025 年後陸續宣布合作架構,即是在這樣的雙軸策略下結合運算與網路設計。對網路與光電產業而言,這意味著:電互連的限制愈來愈明顯,而矽光子與共同封裝光學(CPO)將成為重要的解決方案。

生成式AI帶來的並不只是演算法革命,更是資料中心基礎架構的全面更新。隨著AI模型參數與訓練資料規模呈指數成長,GPU叢集的功率密度與節點數量急速增加,高速互連逐漸成為整體效能與能耗的瓶頸。現代GPU機櫃往往單機櫃就超過100 kW功率,與過去以CPU為主的傳統伺服器機櫃相比,能源與散熱壓力已是完全不同的量級。

在這樣的背景下,AI基礎建設朝Scale-Up與Scale-Out雙路徑演進:一方面提升單一GPU節點與機櫃的算力密度,另一方面則以更多節點構成更大的叢集。OpenAI與NVIDIA、AMD、Broadcom等在 2025 年後陸續宣布合作架構,即是在這樣的雙軸策略下結合運算與網路設計。對網路與光電產業而言,這意味著:電互連的限制愈來愈明顯,而矽光子與共同封裝光學(CPO)將成為重要的解決方案。

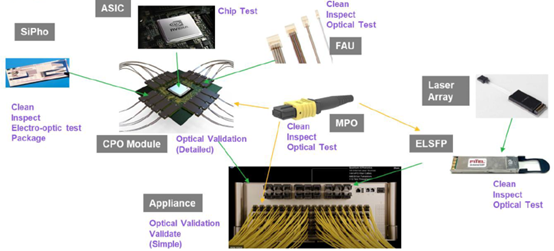

圖1CPO對整個矽光子的生態系統產生相當大的影響;資料來源:翔宇科技

從銅線到矽光子:功耗與佈線逼出新架構

根據Broadcom 的分析顯示,當線路速率從數十Gbps 躍升到100G、200G甚至更高時,銅線在走線長度、損耗與調變複雜度上都面臨急遽惡化的問題;為了維持訊號品質,設計者不得不增加均衡、重計時等電路(equalization and retiming circuits),結果是更多功耗與更高成本。

相較之下,矽光子將光學元件直接整合在矽基板上,可以在晶片或封裝層級完成光訊號的產生、導引與偵測,大幅縮短高頻電訊號走線長度,將瓶頸從「電」轉移到較易延伸的「光」。傳統可插拔光模組的功耗約在 20 pJ/bit 等級,而CPO則有機會把每 bit 能耗壓低到 5 pJ/bit 以下,同時提升頻寬密度並簡化佈線。這不只是節能訴求,更是讓 AI 叢集在機櫃與機房有限的電力預算內塞進更多算力的必要條件。

CPO與LPO 的世代接力:市場預測透露的節奏

在實際導入節奏上,矽光子與CPO並不是孤立前進。產業並非以「一夕取代」可插拔光模組的方式導入CPO,而是分階段演進。過去一段時間,LPO(Linear-drive Pluggable Optics)因沿用可插拔型態、導入風險相對較低,並在部分速率世代提供接近的功耗效益,確實讓CPO的全面爆發時程被往後推,但是當每通道速率進一步推進至 200G-per-lane 等級時,CPO交換器會從特定場景開始逐步擴大。產業諮詢公司Light Counting認為200G-per-lane 的CPO交換器即將到來,並點名從 NVIDIA的 InfiniBandCPO交換器從2025年下半年起跑、後續由 Broadcom 等推進。

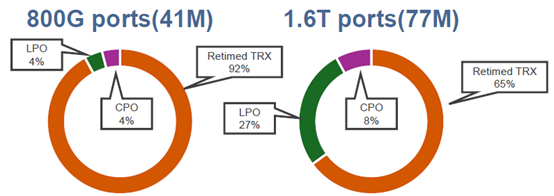

針對800G、1.6T與3.2T乙太網路收發器埠數的出貨構成:在800G時代,Retimed可插拔模組仍佔壓倒性多數,LPO 與CPO僅扮演少數角色;到了 1.6T,LPO 比重明顯升高,而CPO開始佔有可觀但仍相對有限的比例;真正明顯翻轉出現在3.2T世代,CPO在預測中上升為主角之一,Retimed與LPO則相對退居次要,如圖2所示。

圖2CPO與LPO比重逐漸增加;資料來源:翔宇科技

從產業趨勢來看,首先產業會選擇風險較低的LPO 作為過渡解決方案,在熟悉線性驅動與功耗管理後再往CPO推進;其次當線速與頻寬密度來到某個臨界點,只有把光放進封裝、貼近 ASIC,才有足夠的功耗與訊號完整性空間。換句話說,沒有要不要用CPO的問題,而是什麼時候、在哪些應用場景先上。

從架構到現場:CPO生態系的測試壓力

然而,矽光子與CPO真正困難的地方,往往不是概念,而是現場實作。在CPO生態系中,從矽光子晶片(SiPh)、ASIC、光纖陣列單元(FAU)、雷射陣列、ELSFP 光源模組、MPO連接器,一直到CPO模組與最終設備,每一個節點都需要被測試。

這帶來幾項關鍵挑戰:

- 光源穩定性與長期可靠度必須被量化,尤其是ELSFP這類作為共享光源的雷射模組,一旦失效會影響整個系統。

- 可拆卸式FAU雖大幅提升系統靈活性,但其對準精度、封裝良率與對接偏差,會直接反映在插入損耗與錯誤率上。

- 測試層級從wafer、die一直到 module、system,導致驗證流程高度複雜,且現階段缺乏統一標準與完全自動化流程,容易延長開發週期。

對工程師而言,這也意味著心態與工具都要轉換:從過去習慣的看示波器眼圖、量電參數,轉變為解析光譜、光功率分布與多通道光學性能。

隨著光子晶片設計日益複雜,測試流程必須與之共同演進,才能確保光積體電路(Photonic Integrated Circuit, PIC)的性能與可靠度,同時壓低開發與製造成本。其核心觀念是:盡可能把功能與參數測試前移,在晶圓與封裝前階段就及早攔截問題,而不是等到貴重的封裝與模組都完成後才發現異常。

在晶圓測試階段,透過 grating coupling 或 edge coupling 方式,配合可掃描波長的光源與光功率量測模組,就能對波導損耗、響應度、偏振相關損耗(PDL)等進行初步評估。典型的 PIC 晶圓測試架構是以 MAP Swept Wavelength System 搭配探針台與 Source Meter,由控制電腦協調掃描與量測,讓光學與電性的測試在同一流程中完成。

這樣作一是可以縮短整體量測時間與步驟數量,二可以是將功能性測試與製程參數更緊密連結,讓設計與製程工程師能透過數據快速迭代,而不是事後「猜測」問題來源。

別忽略「最小的那一面」:連接器與 FAU 的清潔與檢查

值得一提的是,在CPO與高密度光模組架構中,連接器與 FAU 端面的潔淨度經常被低估,纖芯端面檢查與清潔的重要性,在未來的矽光子技術發展上也會有重大的影響。從實驗室到量產線,都必須建立標準化流程:使用探針式顯微鏡檢查端面是否有灰塵或刮痕,搭配自動化清潔設備(例如 CleanBlast Pro),在不過度耗費擦拭材料的前提下,確保每一次插拔都處於乾淨可用的狀態。

對CPO而言,這不只是維護問題,而是可靠度與良率的關鍵一環:任何微小污染都可能在高功率光源下演變為局部熱點,進而導致端面損傷乃至整體模組退化。因此,把「清潔與檢查」納入正式的量測與製程節點,而不是當作事後補救,是未來高階光電產線必須正視的課題。

從做出CPO,到讓CPO真正「可量產」

矽光子與CPO的技術路線已經確立,市場也在 AI 與高速網路的推動下加速往前;真正決定成敗的,不再是「做不做得出來」,而是「能不能在合理成本下穩定量產」。

要達成這個目標,產業需要在架構上利用CPO與矽光子突破電互連限制;在流程上把測試與驗證前移,從晶圓就開始攔截風險;在工具上導入可擴展、可自動化、能覆蓋從波導到模組乃至系統層級的量測平台。

對台灣的光電與半導體供應鏈而言,這同時是一個挑戰與機會:誰能最先把量測深度整合進矽光子與CPO的設計、製程與封裝流程,誰就更有機會在下一世代的 AI 基礎建設中,佔據關鍵而不可取代的位置。

隨著光子晶片設計日益複雜,測試流程必須與之共同演進,才能確保光積體電路(Photonic Integrated Circuit, PIC)的性能與可靠度,同時壓低開發與製造成本。其核心觀念是:盡可能把功能與參數測試前移,在晶圓與封裝前階段就及早攔截問題,而不是等到貴重的封裝與模組都完成後才發現異常。

在晶圓測試階段,透過 grating coupling 或 edge coupling 方式,配合可掃描波長的光源與光功率量測模組,就能對波導損耗、響應度、偏振相關損耗(PDL)等進行初步評估。典型的 PIC 晶圓測試架構是以 MAP Swept Wavelength System 搭配探針台與 Source Meter,由控制電腦協調掃描與量測,讓光學與電性的測試在同一流程中完成。

這樣作一是可以縮短整體量測時間與步驟數量,二可以是將功能性測試與製程參數更緊密連結,讓設計與製程工程師能透過數據快速迭代,而不是事後「猜測」問題來源。

別忽略「最小的那一面」:連接器與 FAU 的清潔與檢查

值得一提的是,在CPO與高密度光模組架構中,連接器與 FAU 端面的潔淨度經常被低估,纖芯端面檢查與清潔的重要性,在未來的矽光子技術發展上也會有重大的影響。從實驗室到量產線,都必須建立標準化流程:使用探針式顯微鏡檢查端面是否有灰塵或刮痕,搭配自動化清潔設備(例如 CleanBlast Pro),在不過度耗費擦拭材料的前提下,確保每一次插拔都處於乾淨可用的狀態。

對CPO而言,這不只是維護問題,而是可靠度與良率的關鍵一環:任何微小污染都可能在高功率光源下演變為局部熱點,進而導致端面損傷乃至整體模組退化。因此,把「清潔與檢查」納入正式的量測與製程節點,而不是當作事後補救,是未來高階光電產線必須正視的課題。

從做出CPO,到讓CPO真正「可量產」

矽光子與CPO的技術路線已經確立,市場也在 AI 與高速網路的推動下加速往前;真正決定成敗的,不再是「做不做得出來」,而是「能不能在合理成本下穩定量產」。

要達成這個目標,產業需要在架構上利用CPO與矽光子突破電互連限制;在流程上把測試與驗證前移,從晶圓就開始攔截風險;在工具上導入可擴展、可自動化、能覆蓋從波導到模組乃至系統層級的量測平台。

對台灣的光電與半導體供應鏈而言,這同時是一個挑戰與機會:誰能最先把量測深度整合進矽光子與CPO的設計、製程與封裝流程,誰就更有機會在下一世代的 AI 基礎建設中,佔據關鍵而不可取代的位置。